| Creating Value Leveraging Knowledge Earlier known as B. V. B. College of Engineering & Technology | FORM ISO 9001: 2008 – BVBCET School of Electronics | Document #: FMCD2005 | Rev: 1.0 |

|---------------------------------------------------------------------------------------------------|----------------------------------------------------|----------------------|----------|

| Title: Curriculum structure semester wise                                                         | Page 1 of 89                                       |                      |          |

| Electronics and Communication Engineering                                                         |                                                    |                      | Year:    |

# Batch 2021-25 Course Content

| Course Code: 18EECF101    | Course Title: Basic Electronics ( Electrical Stream) |                      |  |

|---------------------------|------------------------------------------------------|----------------------|--|

| L-T-P-Self Study: 4-0-0-0 | Credits: 4 Contact Hrs: 50                           |                      |  |

| ISA Marks: 50             | ESA Marks: 50                                        | Total Marks: 100     |  |

| Teaching Hrs: 50          |                                                      | Exam Duration: 3 hrs |  |

| Content                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Hrs    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| Unit – 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |        |

| Chapter 1: Trends in Electronic Industries Introduction, Roadmap of electronic sector, scope and opportunities in various segments of electronics (i.e. Consumer, Telecom, IT, Defense, Industrial, Medical and Automobiles), Government and private sectors, Growth profile of Electronic industries, Standards and Policies, Electronic System Components.                                                                                                                                                                                                                                                    | 03 hrs |

| Chapter 2:Basic components, devices and Applications  Diode: PN junction characteristics; modeling as a circuit element, ideal and practical diode. AC to DC converter: Half wave and full wave rectifier (centre tap and bridge), capacitor filter and its analysis, numerical examples. Zener diode and its applications (Voltage reference and voltage regulator). Realization of simple logic gates like AND and OR gates.                                                                                                                                                                                  | 08 hrs |

| Chapter 3:Transistor  BJT, transistor voltages and currents, Signal amplifier (Fixed bias, Collector base bias, Voltage divider bias, CE configuration). DC load line. Voltage, current and power gains. Transistor as a switch: NOT Gate, Basic (DTL) NAND gate.                                                                                                                                                                                                                                                                                                                                               | 09 hrs |

| /Unit – 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |        |

| Chapter 4:Digital Logic  Number systems: Decimal, Binary, Octal and Hexadecimal number systems, Conversions, Binary Operations-Addition and subtraction in binary number systems. Logic gates: Realization of simple logic functions using basic gates (AND, OR, NOT), Realization using universal gates (NAND, NOR). Boolean algebra: Theorems and postulates, DeMorgan's Theorems, simplification of logical expressions, Karnaugh Maps, Use of Karnaugh Maps to Minimize Boolean Expressions(2 Variables, 3 Variables and 4 Variables), Design of HalfAdder and Full Adder, Parallel Adder using full adders | 13 hrs |

| Chapter 5:Operational Amplifier  OPAMP characteristics (ideal and practical). Concept of positive and negative feedback (At zero frequency). Linear and non-linear applications: Inverting amplifier, Non inverting amplifier, Voltage follower, Integration, Differentiation, Adder, Subtractor, ZCD and Comparator.                                                                                                                                                                                                                                                                                           | 06 hrs |

| Unit – 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |        |

| Creating Value Leveraging Knowledge Earlier known as B. V. B. College of Engineering & Technology | FORM ISO 9001: 2008 – BVBCET School of Electronics | Document #: FMCD2005 | Rev: 1.0 |

|---------------------------------------------------------------------------------------------------|----------------------------------------------------|----------------------|----------|

| Title: Curriculum structure semester wise                                                         | Page 2 of 89                                       |                      |          |

| Electronics and Communication Engineering                                                         | Year:                                              |                      |          |

| Chapter 6: Communication Systems                                                                                                                                                                                                                                                                                                                                        |        |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| Basic block diagram of communication system, types of modulation. Amplitude modulation: Time-Domain description, Frequency-Domain description. Generation of AM wave: square law modulator. Detection of AM waves: envelope detector. Double side band suppressed carrier modulation (DSBSC), Generation of DSBSC wave: balanced modulator, Super heterodyne principle. |        |

| Chapter 7:Linear Power Supply, UPS & CRO Working principle of linear power supply, UPS and CRO. Measurement of amplitude, frequency and phase of a given signal.                                                                                                                                                                                                        | 04 hrs |

## Text Books (List of books as mentioned in the approved syllabus)

- 1) David A Bell, Electronic devices and Circuits, PHI New Delhi,2004

- 2) K.A Krishnamurthy and M.R.Raghuveer, Electrical, Electronics and Computer Engineering for Scientist and Engineers, 2, New Age International Publishers, 2001

- 3) A.P. Malvino, Electronic Principles, 6, Tata McGraw Hill, 1999

- 1) George Kennedy, Electronic Communication Systems, 4, TataMcGraw Hill, 2000

- 2) Morris Mano, Digital logic and Computer design, 21st Indian print Prentice Hall India, 2000

- 3) Floyd, Digital fundamentals, 3, Prentice Hall India, 2001

- 4) Ramakant Gaikawad , Operational Amplifiers & applications, 3, PHI,2000

| Creating Value Leveraging Knowledge Earlier known as B. V. B. College of Engineering & Technology | FORM ISO 9001: 2008 – BVBCET School of Electronics | Document #: FMCD2005 | Rev: 1.0 |

|---------------------------------------------------------------------------------------------------|----------------------------------------------------|----------------------|----------|

| Title: Curriculum structure semester wise                                                         | Page 3 of 89                                       |                      |          |

| Electronics and Communication Engineering                                                         |                                                    |                      | Year:    |

| Course Code: 21EEXF101    | Course Title: Basic Electrical and Electronics<br>Engineering (Mechanical Science) |                      |  |

|---------------------------|------------------------------------------------------------------------------------|----------------------|--|

| L-T-P-Self Study: 4-0-0-0 | Credits: 4 Contact Hrs: 47                                                         |                      |  |

| ISA Marks: 50             | ESA Marks: 50 Total Marks: 100                                                     |                      |  |

| Teaching Hrs: 47          |                                                                                    | Exam Duration: 3 hrs |  |

| Content                                                                                                                                                                                                                                                                                                                                                     | Hrs       |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|--|--|

| Unit – 1                                                                                                                                                                                                                                                                                                                                                    |           |  |  |

| Chapter 1: Introduction to Electrical & Electronics Technology  Electrical Power Generation (convention and renewable energy sources, with PV elaborated), transmission, distribution, utilization (Electric Vehicle as a case study), Electrical and Electronic Systems, concept and power of abstraction, lumped circuit abstraction, and its limitation. | 02<br>hrs |  |  |

| Chapter 2: The Circuit Abstraction  Energy storage and dissipating elements (RLC), Ideal and practical sources, series and parallel circuits, concept of order of the system, voltage dividers, RC, RL, RLC with KCL and KVL, Mesh and Nodal analysis with an example.                                                                                      | 10<br>hrs |  |  |

| Chapter 3: Introduction to Transformer and Electric Drive  Electromagnetic principles, classification of electric machines – static and rotary, transformers, motors, PMDC, stepper, BLDC, single and three-phase induction motors, selection of motors for various applications. Safety measures.                                                          | 10 hrs    |  |  |

| Unit – 2                                                                                                                                                                                                                                                                                                                                                    |           |  |  |

| Chapter No. 4: Semiconductor Devices and its Applications Fundamentals of semiconductors, PN junction diode, BJT, FET, Thyristors, Integrated circuits, Linear application – Transistors and Operational amplifiers, oscillators (Op-Amp based), Nonlinear application – Power electronics converters.                                                      | 10 hrs    |  |  |

| Chapter No. 5: Digital Abstraction  Concept of digital abstraction, Number systems, base conversion – binary, decimal, hexadecimal, BCD, Gray code, Boolean algebra, logic gates, combinational circuits, - half adders, full adders, half subtractor and full subtractor using k-maps for 2 or 3 variables, sequential circuits – registers, counters.     | 10 hrs    |  |  |

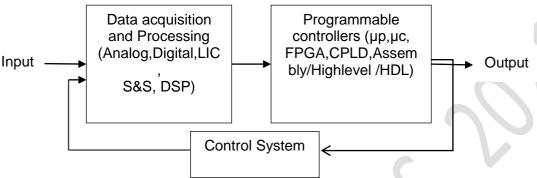

| Chapter No. 6: Mechatronic Subsystem  Power supply, Introduction to sensors and actuators, signal conditioning and interfacing, Control logic design for mechatronic applications.                                                                                                                                                                          | 5         |  |  |

| Creating Value Leveraging Knowledge Earlier known as B. V. B. College of Engineering & Technology | FORM  ISO 9001: 2008 – BVBCET  School of Electronics | Document #: FMCD2005 | Rev: 1.0 |

|---------------------------------------------------------------------------------------------------|------------------------------------------------------|----------------------|----------|

| Title: Curriculum structure semester wise                                                         | Page 4 of 89                                         |                      |          |

# **Text Books (List of books as mentioned in the approved syllabus)**

- 1. Anant Agarwal and Jefferey H. Lang, Foundations of Analog and Digital Electronic Circuits, Morgan Kaufmann -Elsevier, 2005

- 2. Hughes, Electrical and Electronic Technology, 12th Edition, Pearson, 2016.

- N.P.Mahalik, Mechatronics Principles, Concepts and Applications, Tata McGraw-Hill, 2011

- 2. K.A Krishnamurthy and M.R.Raghuveer, Electrical, Electronics and Computer Engineering for Scientist and Engineers, 2, New Age International Publishers, Wiley Eastern, 2001

- 3. George Kennedy, Electronic Communication Systems, 4, Tata McGraw Hill, 2000

- 4. Morris Mano, Digital Logic and Computer Design, 21st Indian print Prentice Hall India, 2000

- 5. Boylestead Nashelsky, Electronic devices & Circuit theory, 6, Prentice Hall India, 2000

- 6. David A Bell, Electronic Devices and Circuits, PHI New Delhi, 2004

- 7. Ramakant Gayakwad, Operational Amplifiers & applications, 3, PHI, 2000

- 8. W.Bolton, Mechatronics Electronic Control Systems in Mechanical and Electrical Engineering, 3, Pearson Education, 2005

- 9. Ernest O Doeblin, Dhanesh N Manik, Measurement Systems, 6th Edition, McGraw Hill Education; 2017

| KLE Technological University Creating Value Leveraging Knowledge Earlier known as B. V. B. College of Engineering & Technology | FORM ISO 9001: 2008 – BVBCET School of Electronics | Document #: FMCD2005 | Rev: 1.0 |

|--------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|----------------------|----------|

| Title: Curriculum structure semester wise                                                                                      | Page 5 of 89                                       |                      |          |

| Electronics and Communication Engineering                                                                                      |                                                    |                      | Year:    |

# Batch 2020-24 Semester: III

| No | Code      | Course                                         | L-T-P  | Credits | Contact<br>Hours | ISA  | ESA | Total | Exam<br>Duration |

|----|-----------|------------------------------------------------|--------|---------|------------------|------|-----|-------|------------------|

| 1  | 15EMAB203 | BS: Integral Transforms and Statistics         | 4-0-0  | 4       | 4                | 50   | 50  | 100   | 3 hours          |

| 2  | 15EECC201 | PC1: Circuit Analysis                          | 4-0-0  | 4       | 4                | 50   | 50  | 100   | 3 hours          |

| 3  | 15EECC202 | PC2: Analog Electronic Circuits                | 4-0-0  | 4       | 4                | 50   | 50  | 100   | 3 hours          |

| 4  | 19EECC201 | PC3: Digital Circuits                          | 4-0-0  | 4       | 4                | 50   | 50  | 100   | 3 hours          |

| 5  | 19EECC202 | PC4: Signals & Systems                         | 4-0-0  | 4       | 4                | 50   | 50  | 100   | 2 hours          |

| 6  | 15EECP201 | PCL1: Digital Circuits Lab                     | 0-0-1  | 1       | 2                | 80// | 20  | 100   | 2 hours          |

| 7  | 15EECP202 | PCL2: Analog Electronic<br>Circuits Lab        | 0-0-1  | 1       | 2                | 80   | 20  | 100   | 2 hours          |

| 8  | 21EECF202 | ES2: Microcontroller                           | 0-0-3  | 3       | 6                | 80   | 20  | 100   | 2 hours          |

| 0  | 18EECF204 | Architecture & Programming C Programming (Dip) | 0-0-2  | 2       | 4                | _    |     |       |                  |

| TO | TAL       |                                                | 20-0-5 | 25      | 32               | 490  | 310 | 800   |                  |

Note: Regular 25 Credit Diploma: 24 Credits

**ISA**: In Semester Assessment **ESA**: End Semester Assessment **L**: Lecture **T**: Tutorials **P**: Practical HS (Humanities) = H; B(Basic Science) = B; ES(Engineering Science) = F; PC (Program Core) = C; EC(Any Elective) = E; PW(Project Work) = W; Research = R; Internship= I; Seminar = S; Colloquium = V; Self-study = Y; Special topic= T; Apprenticeship = A; Laboratory / Practical = Field Work = D; and Non-credit course = N.

| Creating Value Leveraging Knowledge Earlier known as B. V. B. College of Engineering & Technology | FORM ISO 9001: 2008 – BVBCET School of Electronics | Document #: FMCD2005 | Rev: 1.0 |

|---------------------------------------------------------------------------------------------------|----------------------------------------------------|----------------------|----------|

| Title: Curriculum structure semester wise                                                         | Page 6 of 89                                       |                      |          |

| Electronics and Communication Engineering                                                         |                                                    |                      | Year:    |

Semester: IV

| No | Code                   | Course                                                | L-T-P  | Credits | Contact<br>Hours | ISA        | ESA | Total | Exam<br>Duration |

|----|------------------------|-------------------------------------------------------|--------|---------|------------------|------------|-----|-------|------------------|

| 1. | 17EMAB208              | BS: Linear Algebra &Partial<br>Differential Equations | 4-0-0  | 4       | 4                | 50         | 50  | 100   | 3 hours          |

| 2. | 21EECC209              | ES4: Electromagnetic Fields and Waves                 | 3-0-0  | 3       | 3                | 50         | 50  | 100   | 3 hours          |

| 3. | 19EECC203              | PC5: Linear Integrated Circuits                       | 4-0-0  | 4       | 4                | 50         | 50  | 100   | 3 hours          |

| 4. | 15EECC206              | PC6: Control Systems                                  | 4-0-0  | 4       | 4                | 50         | 50  | 100   | 3 hours          |

| 5. | 15EECC207              | PC7: ARM Processor & Applications                     | 3-0-0  | 3       | 3                | 50         | 50  | 100   | 3 hours          |

| 6. | 15EECC208              | PC8: Digital System Design using Verilog              | 0-0-2  | 2       | 4                | 80         | 20  | 100   | 2 hours          |

| 7. | 15EECP203              | PCL3: Data acquisition and controls Lab               | 0-0-1  | 1       | /2               | 80         | 20  | 100   | 2 hours          |

| 8. | 15EECP204              | PCL4: ARM Microcontroller<br>Lab                      | 0-0-1  | 1/      | 2                | 80         | 20  | 100   | 2 hours          |

| 9. | 21EECF201<br>21EECF203 | PCL3: Data Structure<br>Applications Lab              | 0-0-2  | 2       | 4                | 80         | 20  | 100   | 2 hours          |

|    |                        | PCL3: Data Structure Using C<br>Lab(Diploma)          | 0-0-3  | 3       | 6                |            |     |       |                  |

| TO | TAL                    |                                                       | 18-0-6 | 24      | 30               | <b>570</b> | 330 | 900   |                  |

Note : Regular 24 Credit Diploma : 25 Credits

| Technological University Creating Value Leveraging Knowledge Earlier known as B. V. B. College of Engineering & Technology | FORM ISO 9001: 2008 – BVBCET School of Electronics | Document #: FMCD2005 | Rev: 1.0              |

|----------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|----------------------|-----------------------|

| Title: Curriculum structure semester wise<br>Electronics and Communication Engineering                                     |                                                    |                      | Page 7 of 89<br>Year: |

| Program: III Semester B                                                                                       | achelor of Engineering (Electronics & C                                                                                                                                                                           | ommunication Engineering)                                                                                                             |                   |

|---------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| Course Title: Integral tra                                                                                    | nnsforms and Statistics                                                                                                                                                                                           | Course Code: 15EMAB203                                                                                                                |                   |

| L-T-P: 4-0-0                                                                                                  | Credits: 04                                                                                                                                                                                                       | Contact Hours: 4Hrs/week                                                                                                              | Teaching<br>Hours |

| ISA Marks: 50                                                                                                 | ESA Marks: 50                                                                                                                                                                                                     | Total Marks: 100                                                                                                                      | Hours             |

| Teaching Hours: 50Hrs                                                                                         | Examination Duration: 3 Hrs                                                                                                                                                                                       |                                                                                                                                       | ,                 |

|                                                                                                               | Unit I                                                                                                                                                                                                            | ,                                                                                                                                     |                   |

|                                                                                                               | _                                                                                                                                                                                                                 |                                                                                                                                       |                   |

|                                                                                                               |                                                                                                                                                                                                                   | vatives and integrals- Properties. Periodic                                                                                           | 10                |

| Inverse Transforms- pro                                                                                       | -                                                                                                                                                                                                                 | and Final value theorems, examples;                                                                                                   |                   |

| Chapter 2: Probability                                                                                        |                                                                                                                                                                                                                   | /                                                                                                                                     |                   |

|                                                                                                               | conditional probability, Baye's rule, Cheby<br>tions: Binomial, Poisson, Exponential, Uni                                                                                                                         |                                                                                                                                       | 10                |

|                                                                                                               | Unit II                                                                                                                                                                                                           |                                                                                                                                       |                   |

| Chapter 3: Regression: Introduction to method of Engineering problems.                                        | least squares, fitting of curvesy=a+bx,                                                                                                                                                                           | $y = ab^x$ , correlation and regression.                                                                                              | 05                |

| Chapter 4: Fourier Serie                                                                                      | s                                                                                                                                                                                                                 |                                                                                                                                       |                   |

| Complex Sinusoids, Fouri<br>representations, Derivation<br>Convergence of Four<br>Properties of Fourier Serie | er series representations of four classes of<br>on of Complex Co-efficients of Expo-<br>tier Series. Amplitude and phase<br>s(with proof): Linearity, Symmetry Proper<br>iation coefficients, Time domain Convol- | e spectra of a periodic signal.                                                                                                       | 08                |

| Linearity, Symmetry Pro                                                                                       | non-periodic signals, Magnitude and phase perties, Time shift, Frequency Shift,                                                                                                                                   | e spectra. Properties of Fourier Transform:<br>Scaling, Time differential differentiation<br>Parseval's theorem and Examples on these |                   |

| /                                                                                                             | Unit III                                                                                                                                                                                                          |                                                                                                                                       |                   |

| Chapter 6: Random Proc                                                                                        |                                                                                                                                                                                                                   |                                                                                                                                       | 10                |

| 1. Introduction to Joint covariance, correlatio                                                               | Probability Distributions, marginal distrib                                                                                                                                                                       | oution, joint pdf and cdf, mean, variance,                                                                                            |                   |

| 2. Introduction to Ran autocorrelation function                                                               | dom process, stationary process, mear                                                                                                                                                                             | n, correlation and covariance function, ensity: properties of the spectral density;                                                   |                   |

|                                                                                                               |                                                                                                                                                                                                                   |                                                                                                                                       |                   |

| Creating Value Leveraging Knowledge Earlier known as B. V. B. College of Engineering & Technology | FORM  ISO 9001: 2008 – BVBCET  School of Electronics | Document #: FMCD2005 | Rev: 1.0     |

|---------------------------------------------------------------------------------------------------|------------------------------------------------------|----------------------|--------------|

| Title: Curriculum structure semester wise Electronics and Communication Engineering               |                                                      |                      | Page 8 of 89 |

- 1. Kreyszig E., Advanced Engineering Mathematics, , 10th edition, Wiley, 2015

- 2. Gupta S C and Kapoor V K, Fundamentals of Mathematical Statistics, 11<sup>th</sup> edition, Sultan Chand & Sons, 2018

- 3. Walpole and Myers, Probability and Statistics for Engineers and Scientists, ; 9<sup>th</sup>edition, Pearson Education India,2013.

### **References**

- 1. Simon Haykin, Barry Van Veen, Signals and SystemsWiley; Second edition ,2007

- 2. J. Susan Milton, Jesse C. Arnold, Introduction to Probability and Statistics: Principles and

Applications for Engineering and the Computing Sciences, 4<sup>th</sup> edition, TATA McGraw-Hill Edition, 2017

| Program: III Semester Bachelor of Engineering (Electronics & Communication Engineering)                                                                                 |                            |                          |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|--------------------------|--|

| Course Title: Circuit Ana                                                                                                                                               | alysis                     | Course Code: 15EECC201   |  |

| L-T-P-SS: 4-0-0                                                                                                                                                         | Credits: 4                 | Contact Hours: 4Hrs/week |  |

| ISA: Marks: 50                                                                                                                                                          | ESA: Marks: 50             | Total Marks: 100         |  |

| Teaching Hours: 50Hrs                                                                                                                                                   | Examination Duration:3 Hrs |                          |  |

| Chapter 1: Basics                                                                                                                                                       |                            |                          |  |

| Active and passive circuit elements, Voltage & current sources, Resistive networks, Nodal Analysis, Super node, Mesh Analysis, Super mesh, Star – Delta Transformation. |                            |                          |  |

| [ Text 1: Chapter 4,5, 7]                                                                                                                                               |                            |                          |  |

| Chapter 2: Network The<br>Homogeneity, Superposit<br>Transfer Theorem, Miller                                                                                           | 08                         |                          |  |

| [Text 1 : Chapter 5]                                                                                                                                                    |                            |                          |  |

| Chapter 3: Network topo<br>Graph of a network, Conce<br>Formulation of Equilibrium<br>]                                                                                 | 04                         |                          |  |

| Creating Value Leveraging Knowledge Earlier known as B. V. B. College of Engineering & Technology | FORM ISO 9001: 2008 – BVBCET School of Electronics | Document #: FMCD2005 | Rev: 1.0              |

|---------------------------------------------------------------------------------------------------|----------------------------------------------------|----------------------|-----------------------|

| Title: Curriculum structure semester wise<br>Electronics and Communication Engineering            |                                                    |                      | Page 9 of 89<br>Year: |

| Unit II  Chapter 4: Two Port Networks  Two port variables, Z,Y, H,G, A- Parameter representations, Input and output impedance calculation, Series, Parallel and Cascade network connections, and their (suitable) models.  [Text 2 : Chapter 11]                                                                                                                                                                                                           | 06 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Chapter 5: Time and Frequency domain Representation of Circuits  Order of a system, Concept of Time constant, System Governing equation, System Characteristic equation, Initial conditions, Transfer Functions (Fourier and Laplace domain representation) [Text 2: Chapter 4]                                                                                                                                                                            | 06 |

| Chapter 6: First order circuits  Transient response of R-C and R-L networks (with Initial conditions)  Concept of phasor, Phasor diagrams, Frequency response characteristics, Polar plots R-C, R-L circuits as differentiator and integrator models, time and frequency domain responses R-C, R-L circuits as Low pass and high pass filters [Text 2: Chapter 5, Text 1: Chapter 8,9,10]                                                                  | 08 |

| Unit III  Chapter 7: Higher order circuits  HigherorderR-C,R-L,andR-L-Cnetworks,timedomainandfrequencydomainrepresentation, Phasor diagrams, Polar and logarithmic plots, Series R-L-C circuit, Transient response, Damping factor,Quality factor, Frequency responsecurve, Peaking of frequency curve and its relation to damping factor, Resonance Parallel, R-L-C circuit, Tank circuit, Resonance, Quality factor and Bandwidth  [Text 2: Chapter 7,8] | 12 |

- 1. W H Hayt, J E Kemmerly, S M Durban, "Engineering Circuit Analysis" McGraw Hill Education; Eighth edition, 2013

- 2. M E. Van Valkenburg, Network Analysis, Third edition Pearson Education, 2019

- 1. Joseph Edminister, Mahmood Nahavi, Electric Circuits, 5th edition, McGraw Hill Education, 2017

- 2. V. K. Aatre, —Network Theory and Filter Design, 3rd edition, New Age International Private Limited, 2014

| Creating Value Leveraging Knowledge Earlier known as B. V. B. College of Engineering & Technology | FORM  ISO 9001: 2008 – BVBCET  School of Electronics | Document #: FMCD2005 | Rev: 1.0      |

|---------------------------------------------------------------------------------------------------|------------------------------------------------------|----------------------|---------------|

| Title: Curriculum structure semester wise                                                         |                                                      |                      | Page 10 of 89 |

| Program: III Semester Bachelor of Engineering (Electronics & Communication Engineering) |  |

|-----------------------------------------------------------------------------------------|--|

|-----------------------------------------------------------------------------------------|--|

| Course Title: Analog Elect                                                                                                                                                                                                                                                                               | ronic Circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Course Code: 15EECC202                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| L-T-P: 4-0-0                                                                                                                                                                                                                                                                                             | Credits: 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Contact Hours: 4Hrs/week                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Teachig |

| ISA Marks: 50                                                                                                                                                                                                                                                                                            | ESA Marks: 50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Total Marks: 100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Hours   |

| Teaching Hours: 50Hrs                                                                                                                                                                                                                                                                                    | <b>Examination Duration: 3 Hrs</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |

|                                                                                                                                                                                                                                                                                                          | Unit I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |

| Chapter 1: Applications of                                                                                                                                                                                                                                                                               | a Junction diode:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0.6     |

| Recap of diode models: piece signal model.                                                                                                                                                                                                                                                               | ee-wise linear model, constant vol                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | tage drop model, ideal diode model, small                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 06      |

| Applications of diodes as a                                                                                                                                                                                                                                                                              | Clipping circuit and clamping circ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | cuits Voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |

| doubler. (T1 : 2.2,2.3.1 to 2                                                                                                                                                                                                                                                                            | 2.3.8,2.6.1to 2.6.3.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | /                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |

| collector voltage-the early e operation as a switch. DC lo comparison of bias circuit, s analysis of BJT circuits-cou bypassed emitter resistor. (T 3.3.4)  Chapter 3: MOSFETs st voltage, creating a channel of the id-vds relationship, the transistor in the sub three characteristics, finite output | ffect large signal operation-the trade line and bias point, base-bias, mall signal models of bipolar trarpling and bypass capacitor, Commit: 3.1.1, 3.2.1,3.2.2, 3.2.3, 3.2.4,  ructure and physical operation for current flow, applying small very P-channel MOSFET, complementation of the production of | emitter characteristics, Dependence of Ic on the ansfer characteristics, the amplifier gain, collector to base bias, voltage divider, existors, two port modeling of amplifiers, ac mon emitter circuit analysis, CE circuit with un-3.3.1, 3.3.2,  The Device structure, operation with no gate rds, operation as vds is increased, derivation of mentary MOS or CMOS, operating the most haracteristics: circuit symbol, the id vsvds eristics of the p-channel MOSFET, the role of vn and input protection. MOSFET circuits at | 07      |

|                                                                                                                                                                                                                                                                                                          | Unit II                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 08      |

| Chapter 4:Biasing of MOSFETs  MOSFET circuits at DC. Biasing in mos amplifier circuits,:By fixing VGS;By fixing VG;With drain to gate feedback resistor;Constant current source biasing and Numericals (T1:4.3)                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |